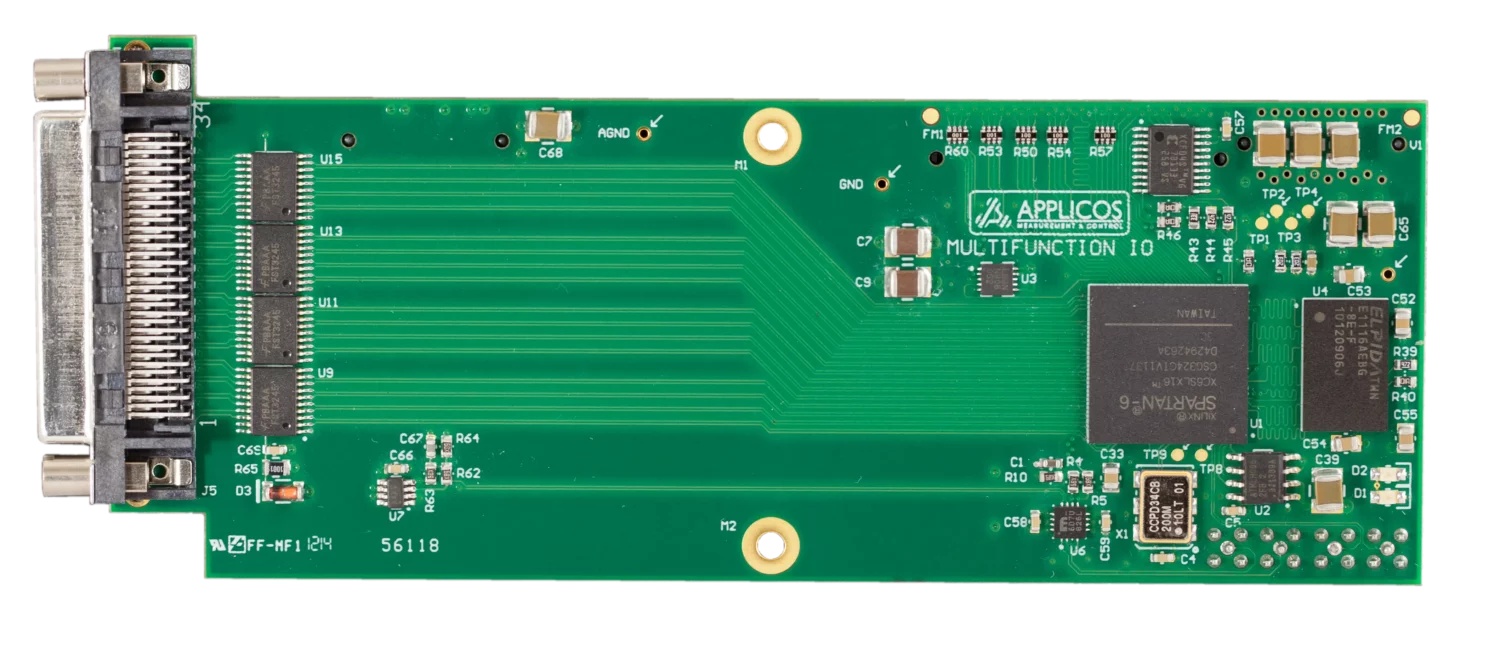

ANALOG BENCH ATE

APPLICOS PA72DIOS6016 Digital Design Core

The PA72DIOS6016 is a multifunctional digital design core.

The FPGA allows for implementing many different custom applications. The connector has 64 Input/Output pins which can be assigned as TTL I/O or as differential inputs. 128 MByte of DDR2 memory is available to the FPGA, and an onboard EEPROM allows for storing values in non-volatile memory. The I/O bank voltage can be FPGA-selected between 2.5 and 3.3 Volt.

Technical Specificatons

| FPGA | Xilinx Spartan6 XC6SLX16 |

| Logic cells | 14579 |

| CLB Flip-Flops | 18224 |

| Front connector | VHDCI SCSI-5 |

| Max. TTL/LVCMOS I/Os | 32 |

| Max. differential inputs | 32 |

| Max. differential outputs | 10 |

| I/O voltages | 2.5V and 3.3V |

| I/O configurations | LVTTL, LVCMOS, PCI, SSTL, (B)LVDS*, LVPECL*, and more. |

| DDR Memory size | 1Gbit |

| DDR Memory frequency | 800MHz |

| Total block RAM | 576kBit |

| Block RAM max. frequency | 320MHz |

* Differential signals as input only