# Challenges In High Voltage IC Design for ATE Applications

Test Technology Symposium 2019 Jef Thoné – Mike Wens

## MinDCet: Power Conversion ASIC Design and Production, ISO9001

## Turnkey Power ASIC Production

Power Module Development

ASIC Design and Layout

MADMIX/MADCAP

Inductor/capacitor measurement

## Measurement capabilities

#### In house

- Recent Investments Q2 2019:

- Teradyne ETS-88 ATE for smooth flow from characterization to production testing

- Chroma FT3110S pick & place handler for smallvolume in-house tri-temp (-40°C-150°C) testing and pre-production testing

- Available from Q4 2019

#### Measurement systems under development

- MADCAP: non-linear large signal capacitor measurements, expected Q1 2020

- MADTHOR: 200V transistor analysis system (capacitance analysis and transistor curves), Q2 2020

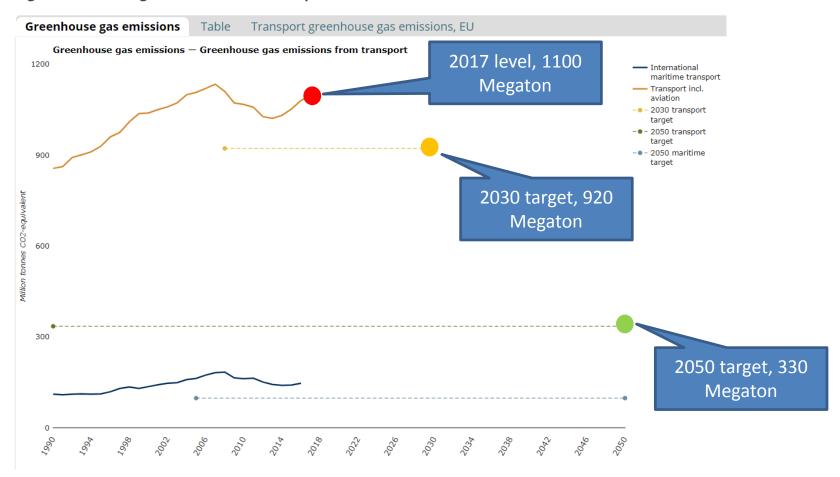

## EU Targets Greenhouse Gas Emission

Fig. 1: Greenhouse gas emissions from transport

https://www.eea.europa.eu/data-and-maps/indicators/transport-emissions-of-greenhouse-gases/transport-emissions-of-greenhouse-gases-11

## EV and WideBandgap

#### X-factor applications

ST / Cree SiC FETs

Model 3 inverter. Note two rows of rectangular devices

Taken from Motor Trend photos of Munro Ass. teardown

TTS 2019 confidential

## **WBG** properties

- Adoption of WBG (wide-bandgap) materials (SiC and GaN) improve efficiency of electrical drives

- Faster switching / less reverse recovery => reduced switching losses

- But : specific gate driver / isolator / isolated supplies / DC bus are needed

- > 2CV with a Ferrari engine: bad idea

ATE need to have similar or better specs than supporting WBG components

#### Ideal interface switch

•

$$R_{on} = 0$$

- $R_{off} = inf.$

- L = 0

- C = 0

- Imax = Inf

- Vmax = inf.

- Area = 0

- Rth = 0

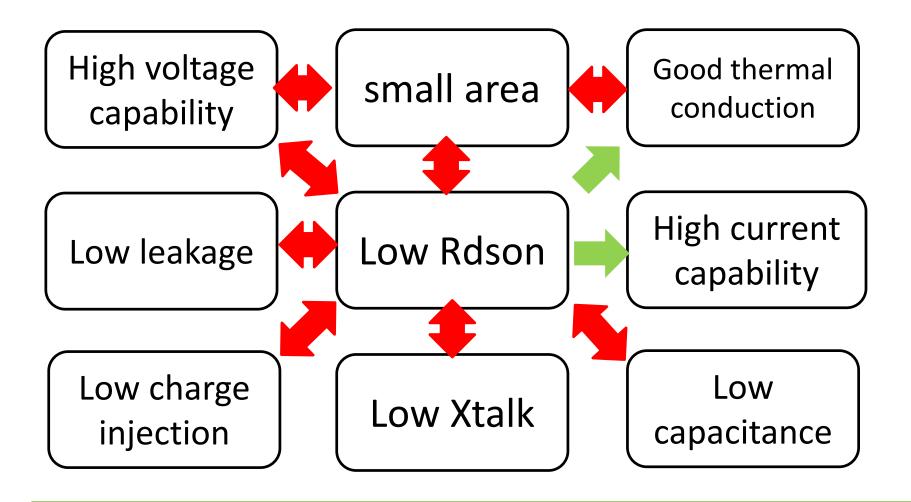

## Opposing interface requirements

## What is a good compromise?

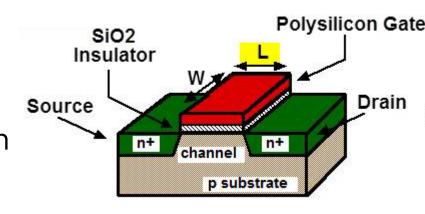

## Low R<sub>dson</sub>

- Rationale:

- Conduction losses

- RC

- Diode conduction at rated I

- By :

- Large W/L: R<sub>dson</sub> ~ L/W

- Dependencies:

- Area ~ L\*W (cost)

- Interconnect (metallization and bonding)

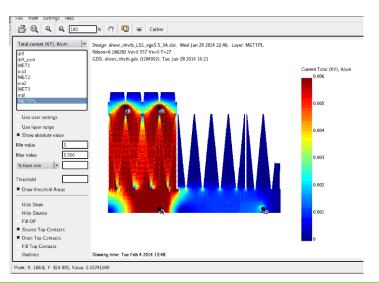

## High current capability

- Rationale:

- Conduct current within EM limits

- By:

- Distributed current

- Custom layout

- Common sense + FEA

- > R3D (Silicon Frontline)

- Magwell

- Dependencies:

- Metallization EM limits

- Area / aspect ratio

- Packaging

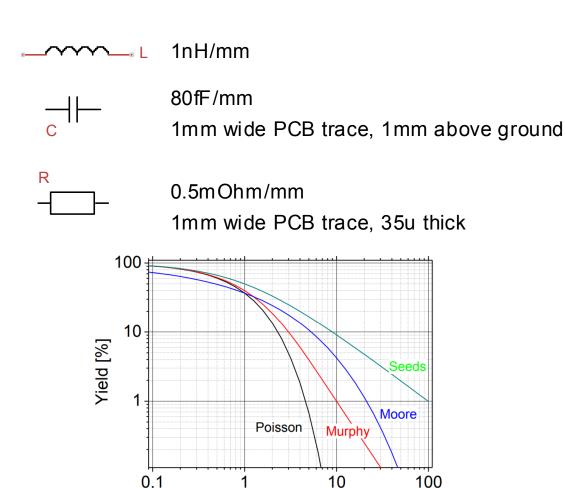

#### Small Area

- Rationale

- Multi channel integration

- Low C, L and R

- By

- Architecture

- Technology (Si, GaN, SiC, hybrid, ...)

- Dependencies

- Die yield ~ exp^-Area

- Thermal conduction ~ Area

AD (critical area A \* defect density D)

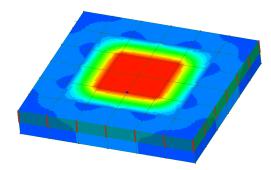

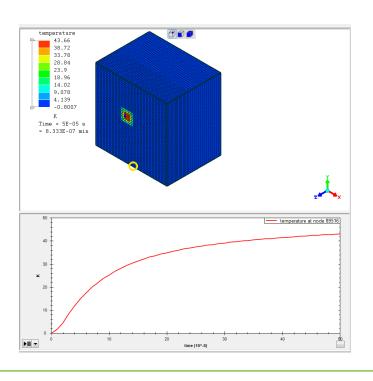

#### Good thermal conduction

- Rationale:

- Keep Tj under control (lifetime)

- By:

- Area/dimensions

- material stack

- Package choice

- FEA thermal simulation (transient/static)

- Dependencies:

- Transient power peaks

- Driver location

- Thermal interface materials

- Tech choice

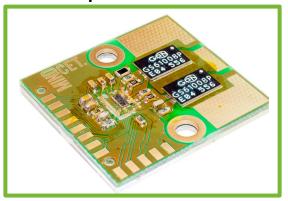

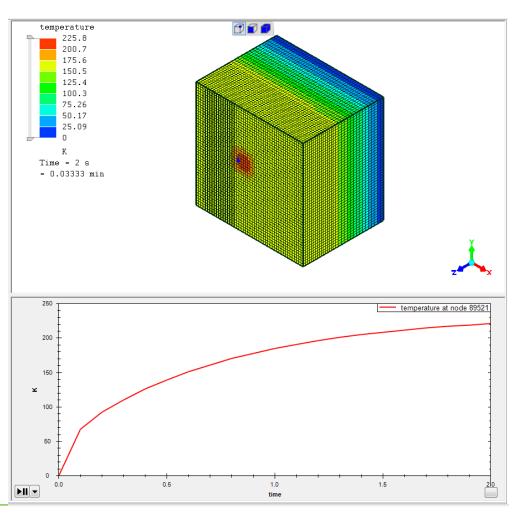

#### Good thermal conduction

Custom

Integrated Power

Management

Solutions

E.g. 0.06mm<sup>2</sup> driver on 4mm<sup>2</sup> Si die

- dT @ 2us = 4.5 K

- dT @ 2 s = 225 K

TTS 2019 15

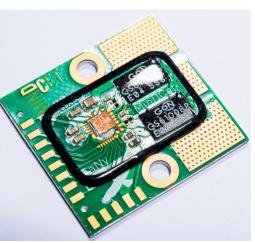

### Good thermal conduction

Packaging is key

## High Voltage Capability

- Rationale:

- Meet the DUT voltage requirements

- By:

- Technology choice

- Custom layouts (metal clearances)

- Custom devices

- Custom DRC

- Hybrid technologies (e.g. GaN-on-SOI)

- Dependencies:

- ~ Area

- SOA operation

- Isolation

- Clearance / creepage beyond package

- ⇔ thermal requirements

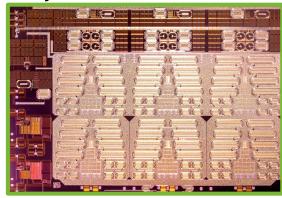

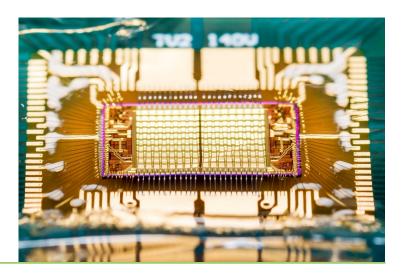

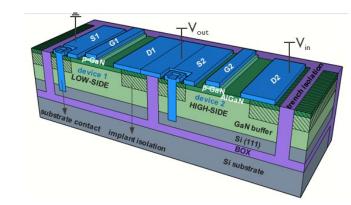

Schematic cross-section of GaN-on-SOI structure, featuring buried oxide, oxide filled deep trench, local substrate contact and p-GaN HEMT devices. Picture courtesy IMEC.

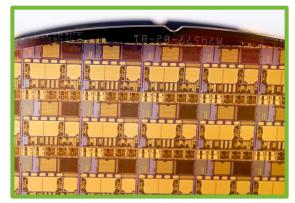

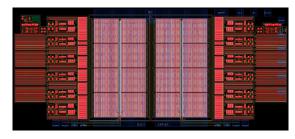

Floorplan of the symmetrical GaNon-SOI 32 mOhm/10A halfbridge

## Low leakage

- Rationale:

- Loading of Hi-Z DUT

- Accuracy of VI measurements

- By:

- Technology choice

- Architectural choices

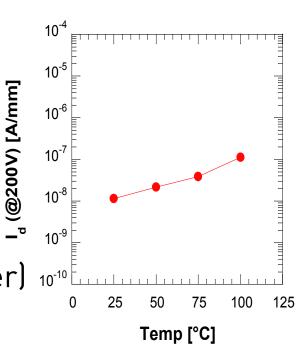

- Leakage cancellation circuits (1st order) 10<sup>-10</sup>

- Calibration

- Dependencies:

- ~ Area

- ~ Exp(Temperature)

GaN on SOI 200V FET Leakage (IMEC)

TTS 2019 confidential 18

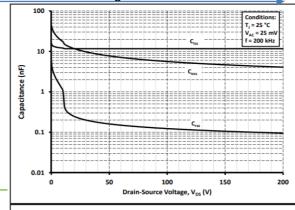

## Low charge injection

- Rationale:

- Limit loading of DUT

- C<sub>iss</sub> → defines gate switching losses

- C<sub>oss</sub> → defines output switching losses

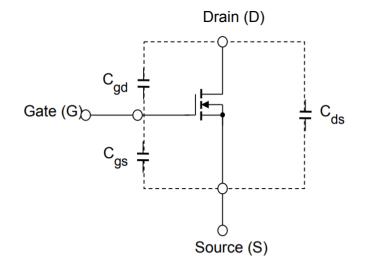

- $C_{rss} = C_{gd}$

- All non-linear vs ds/ gs voltage

Input capacitance  $(C_{iss}) = C_{gd} + C_{gs}$ Output capacitance  $(C_{oss}) = C_{ds} + C_{gd}$ Reverse transfer capacitance  $(C_{rss}) = C_{gd}$

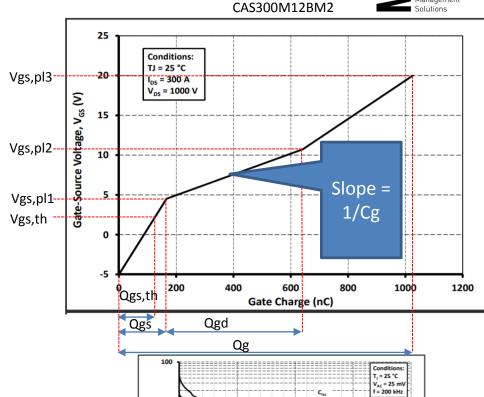

## Definitions of charges

#### JEDEC standard 24-2

•

$$Q_g = Q_{gs} + Q_{gd} + C_{gs}$$

\*  $(V_{gs,pl2} - V_{gs,pl3})$

•

$$Q_{gs,th} = C_{iss} * V_{gs,th}$$

$$Q_{gs} = C_{iss} * V_{gs,pl1}$$

$$Q_{gd} = C_{gs} * (V_{gs,pl1} - V_{gs,pl2})$$

$$+ \int C_{dg}(V). dV_{ds}$$

•

$$Q_{ds} = \int C_{ds}(V) \cdot dV_{ds}$$

•

$$Q_{ci} = Q_{qd} + Q_{ds}$$

- Dependencies:

- Area

- Technology defined!

- Independent of switching speed!

Figure 16. Typical Capacitances vs. Drain-Source Voltage (0 - 200 V)

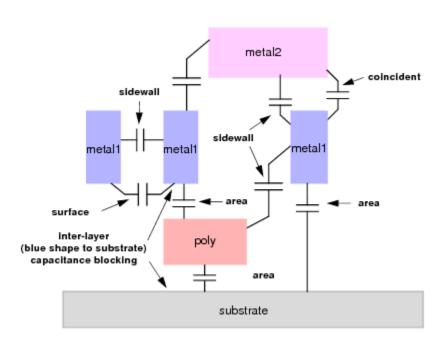

## Low capacitance

- Rationale:

- Limit capacitive loading on the DUT

- Limit charge injection

- Routing can contribute up to 300%

- By:

- Parasitic extraction, post layout

- Smart layout strategies

- Dependencies:

- Process metal stack

#### Low crosstalk

- Rationale:

- Limit distortion of adjacent DUT channels

- Limit loading of high impedance DUT channels

- By:

- Limit interface capacitance

- Low impedant return paths

- Post layout extraction

- Dependencies:

- Metal stack

- Routing impedance

#### Conclusions

- New technology adoption (SiC/GaN) defines future ATE interface requirements

- IC Design of VI's and MUXes for ATE: multi-dimensional design challenge

- If you don't like to make trade-offs :

If you need help to make the trade-offs: call MinDCet!

## What can we do for you?

#### Headquarters

MinDCet NV

Researchpark Haasrode

Romeinse Straat 10

3001 Leuven

Belgium

www.mindcet.com

info@mindcet.com

t: +32 16 40 95 28

t: +32 16 40 14 88

f: +32 16 40 83 38